# **Final Exam**

(December 14<sup>th</sup> @ 7:00 pm)

Presentation and clarity are very important! Show your procedure!

#### PROBLEM 1 (12 PTS)

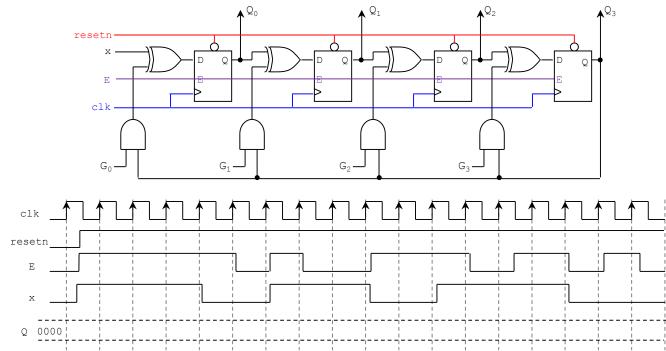

• Complete the timing diagram of the following circuit.  $G = G_3G_2G_1G_0 = 0110$ ,  $Q = Q_3Q_2Q_1Q_0$

## PROBLEM 2 (19 PTS)

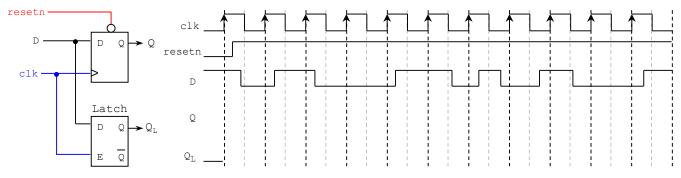

Complete the timing diagram of the circuit shown below: (8 pts)

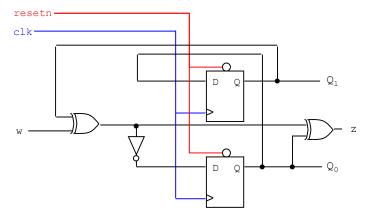

• Provide the State Diagram (any representation), the Excitation Table, and the Excitation equations of the following Finite State Machine: (11 pts)

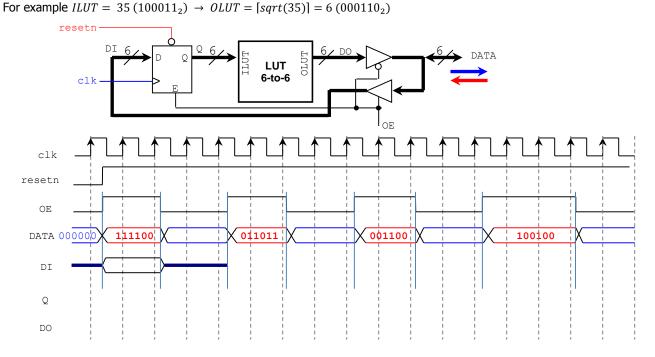

## PROBLEM 3 (10 PTS)

Given the following circuit, complete the timing diagram.

The LUT 6-to-6 implements the following function: *OLUT* = [*sqrt(ILUT)*], where *ILUT* is a 6-bit unsigned number.

#### PROBLEM 4 (23 PTS)

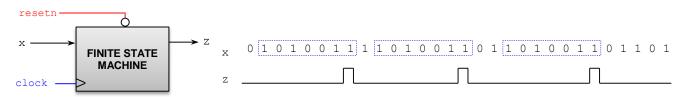

• Sequence detector: The machine has to generate z = 1 when it detects the sequence 1010011. Once the sequence is detected, the circuit looks for a new sequence.

- Draw the State Diagram (any representation), State Table, and the Excitation Table of this circuit with input x and output z. Is this a Mealy or a Moore machine? Why? (15 pts)

- Provide the excitation equations (simplify your circuit using K-maps or the Quine-McCluskey algorithm) (5 pts)

- Sketch the circuit. (3 pts)

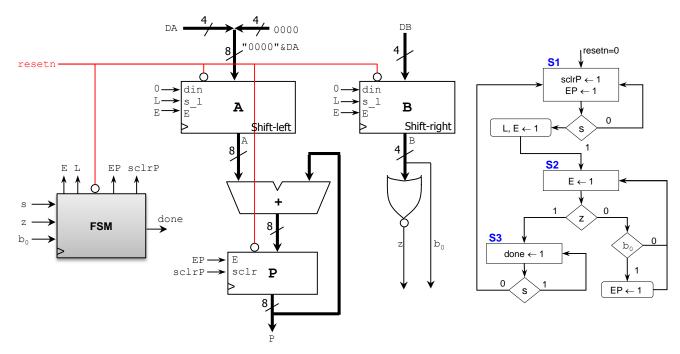

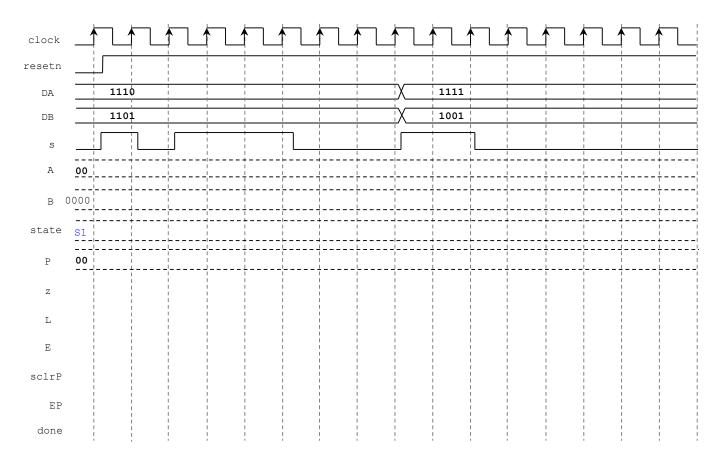

# PROBLEM 5 (20 PTS)

• Complete the following timing diagram (A and P are specified as hexadecimals) of the following Iterative unsigned multiplier. The circuit includes an FSM (in ASM form) and a datapath circuit. Register (for P): sclr: synchronous clear. Here, if sclr = F = 1, the register contents are initialized to 0.

Register (for P): *sclr*: synchronous clear. Here, if *sclr* = E = 1, the register contents are initialized to 0. Parallel access shift registers (for A and B): If E = 1:  $s_l = 1 \rightarrow \text{Load}$ ,  $s_l = 0 \rightarrow \text{Shift}$

## PROBLEM 6 (16 PTS)

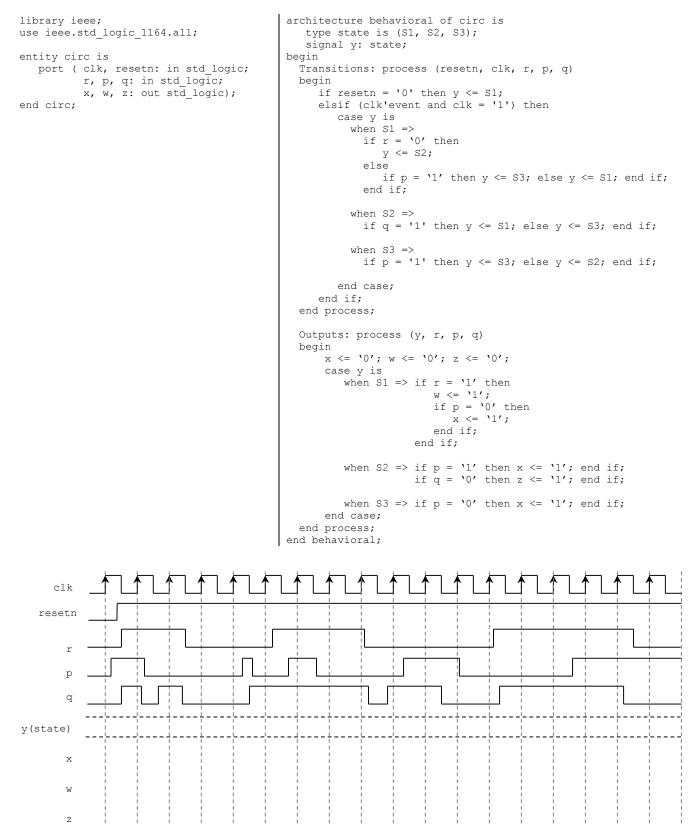

- Draw the State Diagram (in ASM form) of the FSM whose VHDL description in shown below. Is it a Mealy or a Moore FSM?

- Complete the Timing Diagram.